前言:本内容根据《片上互联网络——多核/众核处理器关键技术》中文版自行整理

导论

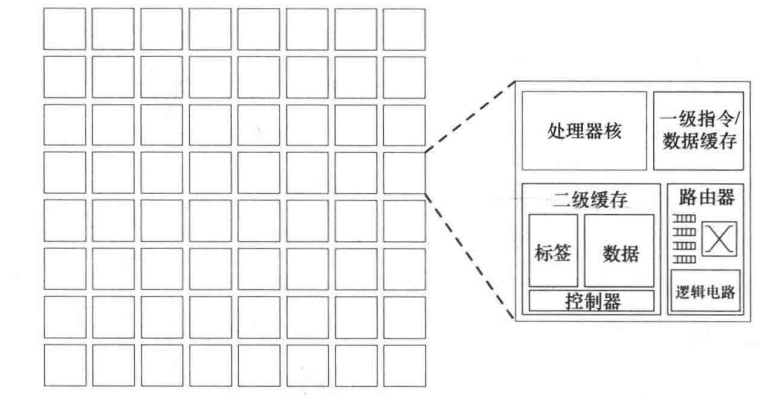

片上网络(On-Chip Networks),也即 NoC,是一种新型的芯片内通信结构,它采用类似计算机网络的设计思想,将片上系统内部的各个处理器、存储器、I/O 等单元连接起来,形成一个可重构的、高效的、灵活的通信网络。

片上网络之前

在 NoC 出现之前,片上系统主要采用总线架构(Bus)或者交叉开关(Crossbar)。

- 总线是一种共享的物理通道,所有处理器核通过同一线路进行通信,同一时间仅允许一对核进行数据传输

- 交叉开关通过矩阵式开关实现任意两个核间的直接连接,支持多对核同时通信

但随着多核处理器(如 MPSoC)和复杂 SoC 的发展,传统架构的局限性愈发明显。总线和交叉开关都无法满足高并发、低延迟、低功耗的需求,促使研究者借鉴计算机网络的分组交换思想,提出了片上网络。

片上网络优势

- 高可扩展性:模块化设计,通过添加路由器和链路可线性拓展节点数量,避免总线架构因节点增加导致的带宽竞争问题

- 高带宽:并行传输

- 低延迟:短距离片上通信和分布式路由算法

片上网络基本构建模块

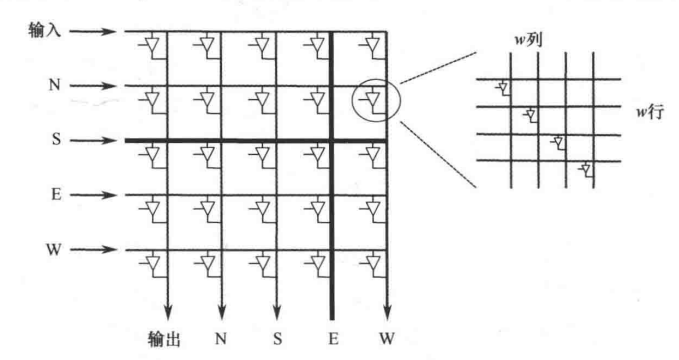

- 拓扑:在网络中各个节点(各个模块连接一个路由器,路由器作为与网络中其他节点的直接对接节点)和通道形成的形状

- 路由:在某种拓扑结构中,消息从源节点到目的节点的走法

- 流控制:消息在传输时需要资源(谁先谁后,通过哪一条路径),流控制规定了给消息分配资源的策略

- 路由器微体系结构:整个路由器工作时需要输入缓冲区、路由器状态、路由逻辑、分配器和交叉开关等部分,这些部分工作的逻辑通常设计为流水线结构

- 链路结构:全摆幅逻辑和带有中继器的连线

片上网络的系统架构接口

共享缓存

在大规模并行处理系统中,结合消息传递接口(Message Passing Interface, MPI)单芯片多处理器(Chip Multiprocessor, CMP)技术,将统一的地址空间划分为多个地址空间分区,每个分区对应多个共享存储的节点,各个分区之间的数据交互通过 MPI 进行统一管理。

实现共享存储的一种方式是共享存储模型:

缓存一致性协议

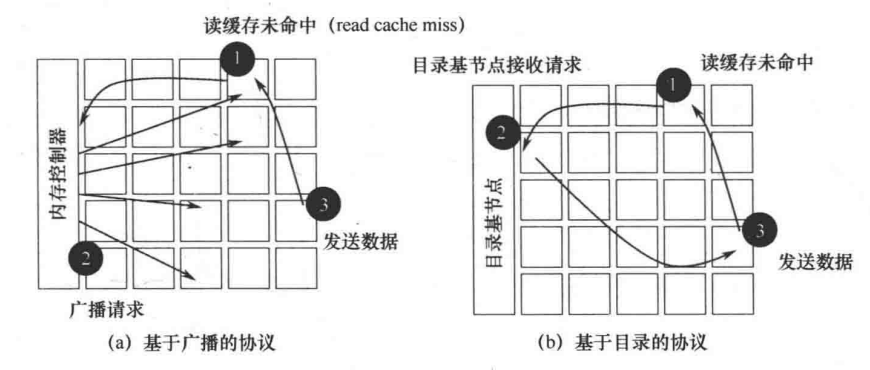

多核系统中常用两种缓存一致性协议:

- 基于广播(broadcast)的协议,常采用 MESI 协议

- Modified

- Exclusive

- Shared

- Invalid

- 基于目录(directory)的协议:中心化目录记录缓存状态

协议级死锁

不同类消息之间存在资源依赖时,就可能导致死锁。

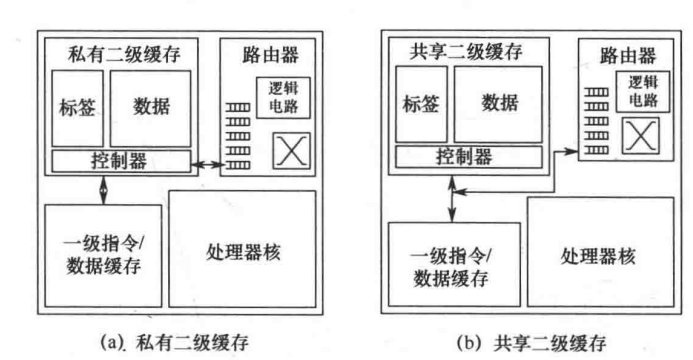

多级缓存

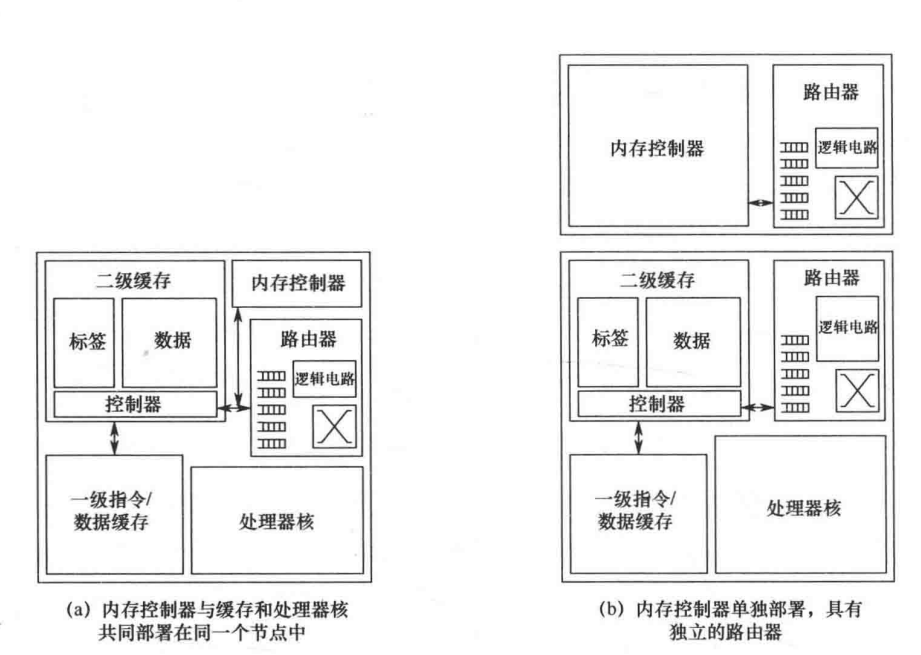

基于目录的协议中的内存控制器

未命中/事物状态保持寄存器 MSHR(Miss Status Holding Register)

- 功能:跟踪未完成缓存未命中请求

- 工作流程:

- 缓存未命中时分配 MSHR 条目

- 合并后续相同地址请求

- 数据返回后批量响应

片上网络接口标准

- 基于总线的事务语义

- 乱序事务

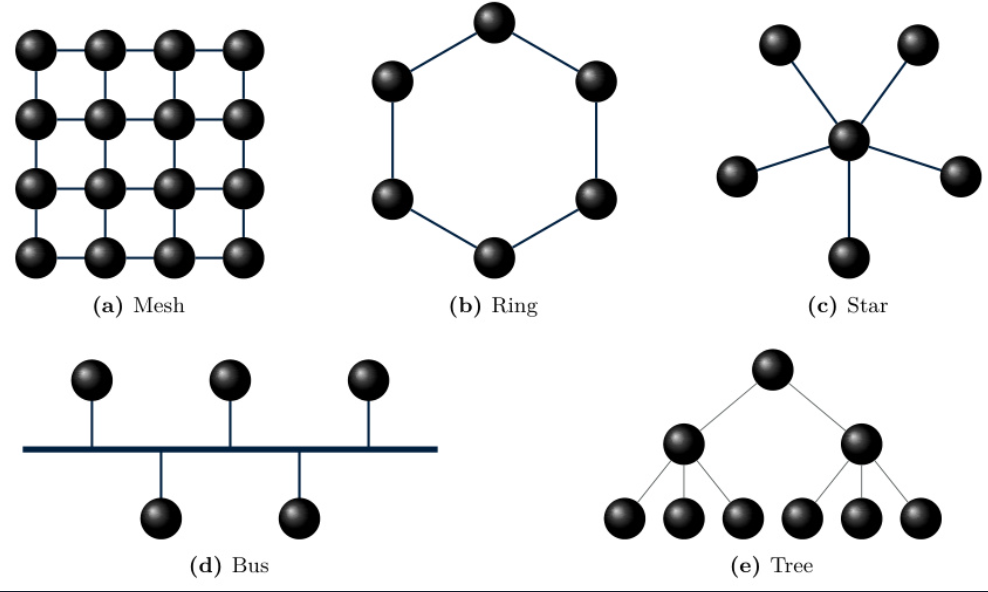

拓扑

| 拓扑类型 | 结构名称 | 连接方式 | 扩展性 | 优缺点 |

|---|---|---|---|---|

| 直连 | Ring | 首尾闭环连接 | 低 | 结构简单无死锁,但带宽受限且扩展性差 |

| 直连 | Mesh | 二维网格布局,四邻连接 | 高 | 规则布局易实现,边缘节点带宽受限,适合平面化制造 |

| 直连 | Torus | Mesh 变体带环绕连接 | 高 | 消除边界效应但布线复杂度增加,需要三维集成技术 |

| 非直连 | Crossbar | N×N 全连接矩阵 | 低 | 零冲突高带宽,但布线复杂度随节点数平方增长 |

| 非直连 | Butterfly | 多级递减式连接 | 中 | 低跳数传输适合大规模系统,但非对称结构导致负载不均衡 |

| 非直连 | Fat Tree | 带宽逐级加粗的树状结构 | 高 | 消除传统树形瓶颈,需要复杂布线且中间层功耗占比高 |

| 混合 | CMesh | 集中式路由连接节点簇 | 高 | 减少全局路由数量但增加本地通信延迟,适合异构计算场景 |

结构特性说明:

- 布线复杂度:与节点连接数和物理距离正相关(Mesh < Torus < Butterfly)

- 功耗分布:非直连拓扑中间节点功耗占比可达 40-60%

- 制造兼容性:Mesh 等平面结构更适合当前 CMOS 工艺

- 容错能力:多路径拓扑(Fat Tree)比单路径(Ring)更易实现故障绕过

路由

| 路由算法种类 | 路由分类 | 实现原理 | 优缺点 |

|---|---|---|---|

| 维序路由 (DOR) | 确定性路由 & 最短路由 | 按维度顺序逐维调整坐标,保证路径最短且无环 | 优点:无死锁、实现简单 缺点:路径固定导致负载不均衡 |

| Valiant 随机路由 | 无关路由 & 非最短路由 | 先将数据包发送至随机中间节点,再从中间节点转发至终点,通过路径随机化打破对称性 | 优点:高容错性 缺点:平均路径长度增加 30%-50% |

| Duato 协议 | 自适应性路由 & 最短路由 | 使用自适应虚拟通道动态选择最短路径,结合逃生通道确保无死锁 | 优点:高吞吐量 缺点:需要额外 2-4 个虚拟通道增加硬件开销 |

| West-First 转向限制路由 | 确定性路由 & 非最短路由 | 限制向西转向必须在路径早期完成,强制形成无环通道依赖图 | 优点:天然避免死锁 缺点:在非对称拓扑中可能产生绕行路径 |

自适应路由的挑战:活锁、维持数据包之间的顺序

选择非最短路径来避免或减少拥塞,往往会比选择存在拥塞的最短路径具有更低的传输延迟。

流控制

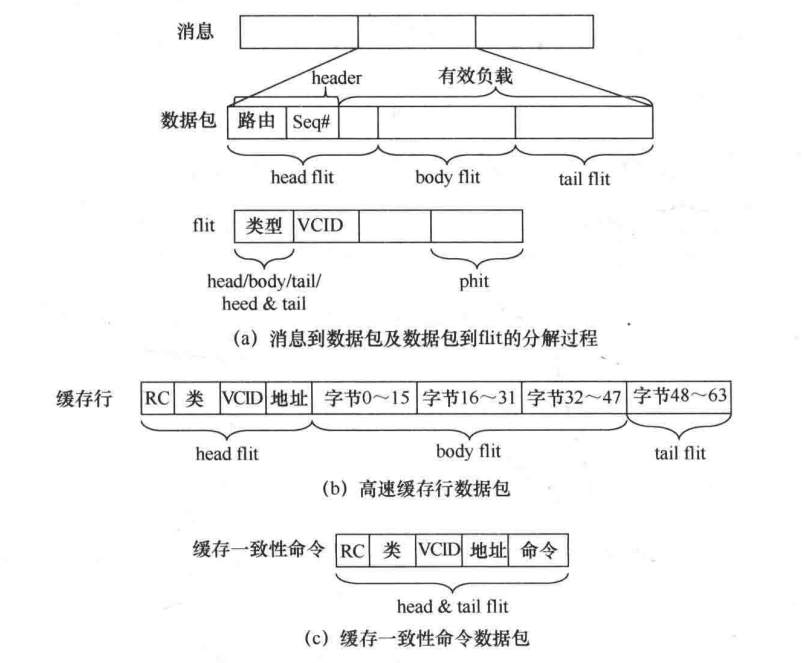

消息、数据包、flit 和 phit

| 层级 | 功能单元 | 典型大小 | 传输方式 | 组成关系 |

|---|---|---|---|---|

| 消息 | 应用层逻辑单元 | 64B-128B | 端到端传输 | 由 1 个或多个数据包组成 |

| 数据包 | 路由基本单元 | 1-5 flit | 逐跳传输 | 头 flit + 体 flit + 尾 flit |

| flit | 流控制基本单元 | 128-256bit | 按虚拟通道管理 | 1 个 flit = 2-4 个 phit |

| phit | 物理传输单元 | 链路宽度(如 64bit) | 每个时钟周期传输 | 不可分割的物理信号单元 |

层级关系:消息 → 拆分为多个包 → 包拆分为多个 flit → flit 拆分为多个 phit

流控制机制

| 机制类型 | 控制级别 | 工作原理 | 主要特性 |

|---|---|---|---|

| 电路交换 (Circuit Switching) | 消息级 | 1. 建立阶段(20-50 周期):协商端到端专用路径 2. 数据传输(固定带宽) 3. 拆除阶段(10-20 周期) |

链路利用率 ≤40% 建立延迟与跳数正相关 |

| 存储转发 (Store-and-Forward) | 数据包级 | 完整接收数据包后校验 CRC32 缓存整个包(1-5KB)再进行路由决策 |

缓冲区需求与包大小成正比 端到端延迟=Σ(传输延迟+排队延迟) |

| 虚拟直通流控制 (Virtual Cut-Through) | 数据包级 | 包头到达立即启动路由计算 采用信用控制保证下一跳缓冲区空间 |

需要至少 1 个包大小的缓冲区 支持提前释放缓冲区 |

| 虫洞交换 (Wormhole Switching) | flit 级 | 1. 头 flit 路由计算(2-3 周期) 2. 体 flit 流水跟进 3. 尾 flit 释放通道资源 |

缓冲区仅需存储 1-3 个 flit 易受跨包队头阻塞影响 |

| 虚拟通道流控制 (VC Flow Control) | flit 级 | 多逻辑通道分时复用物理链路 采用优先级加权轮询调度(如 WRR 算法) |

支持 QoS 差分服务 硬件开销增加 15-20% 需要虚拟通道状态机管理 |

无死锁流控制

| 方法名称 | 原理描述 | 实现方法 | 优势 | 适用场景 | 典型案例 |

|---|---|---|---|---|---|

| 时间线划分 | 通过时间片周期打破资源依赖链 | 将操作划分为奇数/偶数周期,交替使用不同虚拟通道 | 天然避免循环依赖 | 周期性通信场景 | 同步 NoC 架构 |

| 逃生虚拟通道 | 保留专用通道作为逃生路径 | 每个物理通道保留至少 1 个专用逃生 VC,阻塞时启用确定性路由 | 确保死锁可恢复 | 自适应路由网络 | Duato 协议 |

| 气泡流控制 | 环形拓扑中维持空缓冲区防止流量停滞 | 设计时保证环中至少存在 1 个空缓冲区,通过反压机制维持 | 简单有效 | 环形拓扑网络 | 处理器 L2 缓存互连 |

缓冲区反压

| 类型 | 实现方法 | 关键参数 | 优缺点 | 适用场景 | 同步要求 |

|---|---|---|---|---|---|

| 基于 credit | 接收方分配初始信用值,发送方消耗信用,信用耗尽暂停发送 | 初始信用值:8-16 更新延迟:2-3 周期 |

高精度控制但硬件开销大 | 高带宽链路(HBM3 接口) | 严格时钟同步 |

| 基于 ON/OFF 信号 | 接收方通过阈值触发停止/继续信号 | 停止阈值:75%容量 恢复阈值:25%容量 |

低功耗但吞吐量受限 | 低功耗 IoT 芯片 | 宽松同步 |

| 混合方案 | 结合信用机制和全局流控信号 | 信用粒度:VC 级 信号粒度:端口级 |

平衡性能与功耗 | 移动 SoC | 区域同步 |

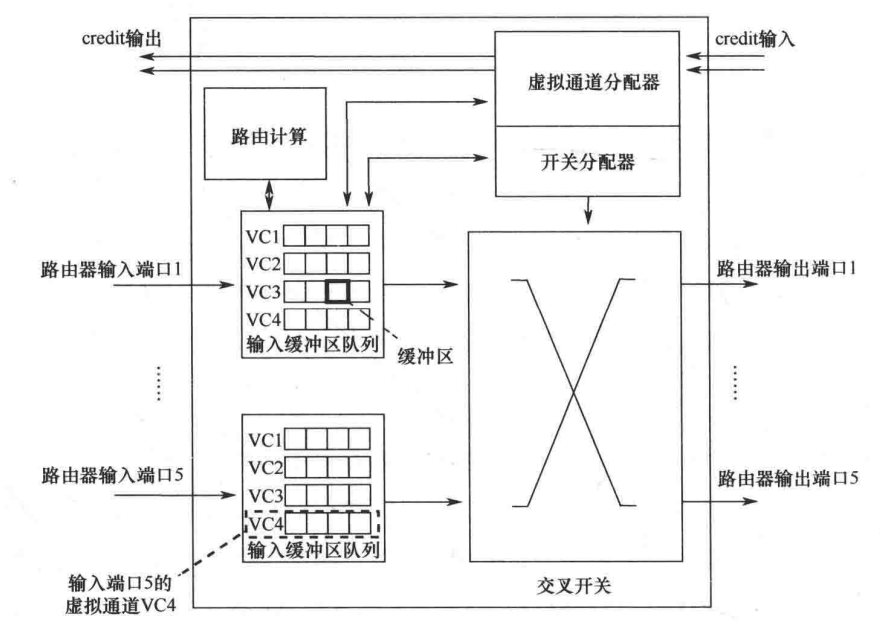

路由器微体系结构

分配器和仲裁器

分配器:将 N 个请求匹配到 M 个资源(如虚拟通道VC或交叉开关端口),支持多对多映射 。

仲裁器:将 N 个请求匹配到 1 个资源 ,解决单一资源的竞争问题。

| 类型 | 类别 | 工作原理 | 优点 | 缺点 |

|---|---|---|---|---|

| 轮询仲裁器 | 仲裁器 | 按固定顺序循环访问请求源,确保每个请求源都能获得均等机会 | 实现简单,公平性有保障 | 无法优先处理紧急请求 |

| 矩阵仲裁器 | 仲裁器 | 通过请求矩阵和授权矩阵进行二维仲裁,支持多请求并行处理 | 高并发处理能力 | 硬件复杂度呈平方增长 |

| 分离式分配器 | 分配器 | 将虚拟通道分配与交叉开关分配分为两个独立阶段 | 减少分配冲突 | 增加流水线级数 |

| 波前分配器 | 分配器 | 采用波前推进算法动态分配资源,优先满足关键路径请求 | 资源利用率高,低延迟 | 需要复杂的状态跟踪机制 |

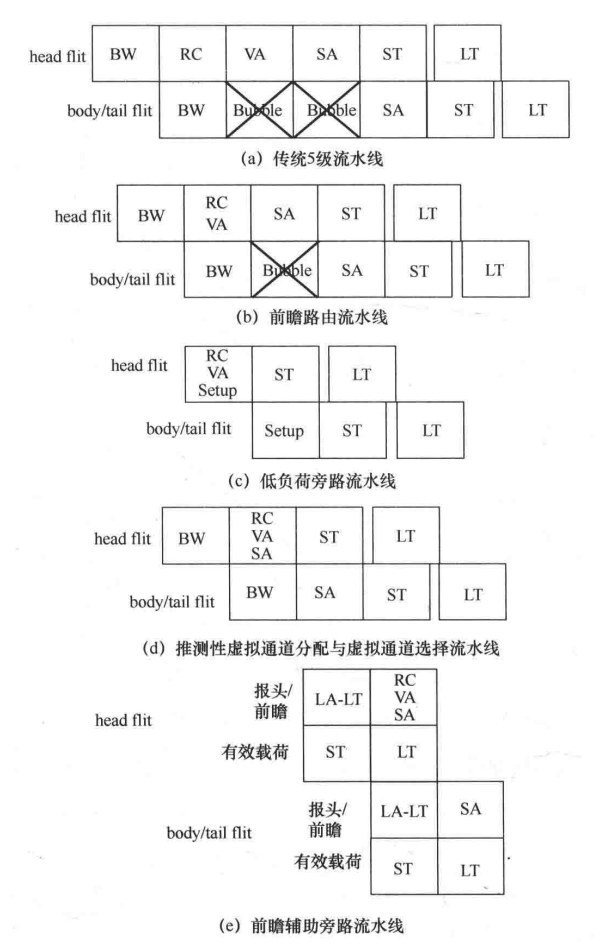

流水线

流水线阶段详解

| 阶段名称 | 功能描述 | 关键参数 | 延迟 | 功耗占比 |

|---|---|---|---|---|

| 缓冲区写入(BW) | flit 物理层数据接收与缓冲 | 缓冲深度:4-8 flit/VC | 0.5-1ns | 8-12% |

| 路由计算(RC) | 确定输出端口和路径 | 路由表条目:256-1024 | 1.2-2ns | 15-20% |

| 虚拟通道分配(VA) | 分配可用虚拟通道资源 | 并发请求数:4-8 | 1.5-3ns | 20-25% |

| 开关分配(SA) | 仲裁输入输出端口连接关系 | QoS 权重:高达 30% | 1.8-3.2ns | 25-30% |

| 交叉开关传输(ST) | 物理层数据交换传输 | 传输位宽:128bit | 0.3-0.5ns | 30-35% |

| 链路传输(LT) | 跨路由器物理链路传输 | 链路频率:2-4GHz | 0.6-1.2ns | 10-15% |

优化技术对比

| 技术名称 | 实现原理 | 性能提升 | 硬件开销 | 适用场景 |

|---|---|---|---|---|

| 前瞻路由计算 | 在 BW 阶段预取路由信息 | 减少 RC 阶段延迟 40% | +5% 逻辑面积 | 高负载网络 |

| 低负荷旁路 | 流量低时跳过 VA/SA 仲裁阶段 | 降低端到端延迟 15-20% | 增加 10%控制逻辑 | 突发流量场景 |

| 动态 VC 合并 | 合并空闲 VC 提升资源利用率 | 吞吐量提升 12-18% | 需要共享缓冲池 | 非均匀流量模式 |